-

Notifications

You must be signed in to change notification settings - Fork 87

Peripheral Access Conventions

bunnie edited this page Sep 26, 2020

·

12 revisions

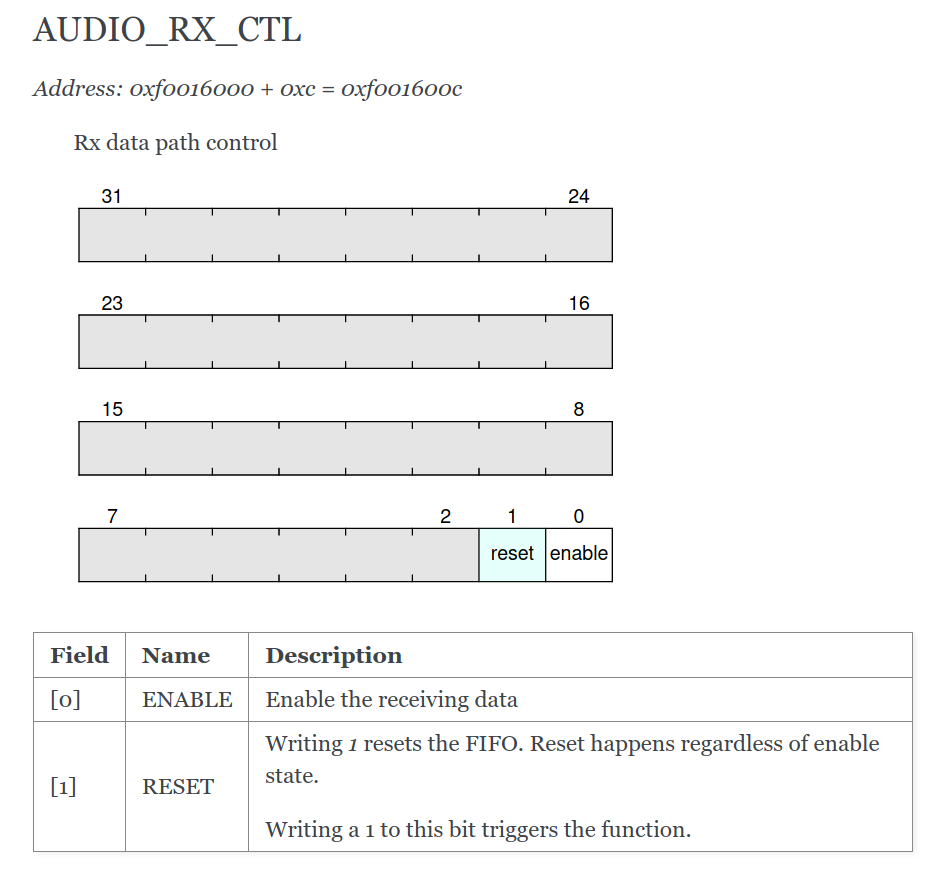

<peripheral>

<name>AUDIO</name>

<baseAddress>0xF0016000</baseAddress>

<groupName>AUDIO</groupName>

<registers>

<register>

<name>RX_CTL</name>

<description><![CDATA[Rx data path control]]></description>

<addressOffset>0x000c</addressOffset>

<resetValue>0x00</resetValue>

<size>32</size>

<access>read-write</access>

<fields>

<field>

<name>enable</name>

<msb>0</msb>

<bitRange>[0:0]</bitRange>

<lsb>0</lsb>

<description><![CDATA[Enable the receiving data]]></description>

</field>

<field>

<name>reset</name>

<msb>1</msb>

<bitRange>[1:1]</bitRange>

<lsb>1</lsb>

<description><![CDATA[Writing `1` resets the FIFO. Reset happens regardless of enable state.]]></description>

</field>

</fields>

</register>

</registers>

</peripheral>csr_base,audio,0xf0016000,,

csr_register,audio_rx_ctl,0xf001600c,1,rw

constant,audio_interrupt,6,,

memory_region,audio,0xe0000000,4,io

// set up the base pointers

let audio_base = (HW_AUDIO_BASE as *mut u32) as *mut Volatile<u32>;

let audio_mem = (HW_AUDIO_MEM as *mut u32) as *mut Volatile<u32>;

// read RX_CTL

let rx_ctl_value = (*audio_base.add(HW_AUDIO_RX_CTL)).r();

// these three proposals all do the same thing: it overwrites the *entire* register with RESET as 0, and the rest as 0 (effectively clears all other bits)

(*audio_base.add(HW_AUDIO_RX_CTL)).ow(HW_AUDIO_RX_CTL_RESET);

(*audio_base.add(HW_AUDIO_RX_CTL)).ow(0, HW_AUDIO_RX_CTL_RESET_MASK, HW_AUDIO_RX_CTL_RESET_OFFSET);

(*audio_base.add(HW_AUDIO_RX_CTL)).ow(False, HW_AUDIO_RX_CTL_RESET_MASK);

// these two proposals manipulates two bits

(*audio_base.add(HW_AUDIO_RX_CTL))

.rw(False, HW_AUDIO_RX_CTL_RESET_MASK, HW_AUDIO_RX_CTL_RESET_OFFSET)

.rw(True, HW_AUDIO_RX_CTL_ENABLE_MASK, HW_AUDIO_RX_CTL_ENABLE_OFFSET);

// actually same as above. The "False" can be dropped with no harm.

(*audio_base.add(HW_AUDIO_RX_CTL))

.rw(True, HW_AUDIO_RX_CTL_ENABLE_MASK, HW_AUDIO_RX_CTL_ENABLE_OFFSET);

// write and read to the audio memory window

(*audio_mem).write( audio_sample );

let mic_data: u16 = (*audio_mem).read() as u16;

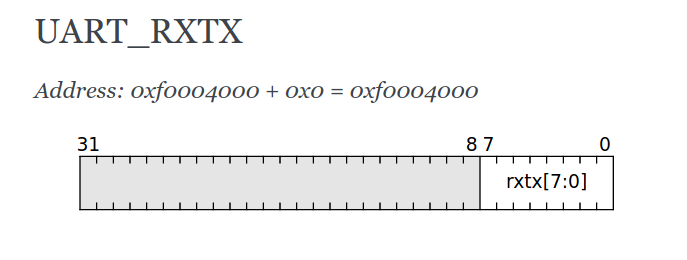

<peripheral>

<name>UART</name>

<baseAddress>0xF0004000</baseAddress>

<groupName>UART</groupName>

<registers>

<register>

<name>RXTX</name>

<addressOffset>0x0000</addressOffset>

<resetValue>0x00</resetValue>

<size>32</size>

<access>read-write</access>

<fields>

<field>

<name>rxtx</name>

<msb>7</msb>

<bitRange>[7:0]</bitRange>

<lsb>0</lsb>

</field>

</fields>

</register>

</registers>

</peripheral>csr_base,uart,0xf0004000,,

csr_register,uart_rxtx,0xf0004000,1,rw

let uart_base = (HW_UART_BASE as *mut u32) as *mut Volatile<u32>;

let rx_char: u8 = (*uart_base.add(HW_UART_RXTX)).r() as u8;

(*uart_base.add(HW_UART_RXTX)).ow(tx_char, HW_UART_RXTX_MASK, HW_UART_RXTX_OFFSET);

(*uart_base.add(HW_UART_RXTX))

.rw(tx_char, HW_UART_RXTX_MASK, HW_UART_RXTX_OFFSET)

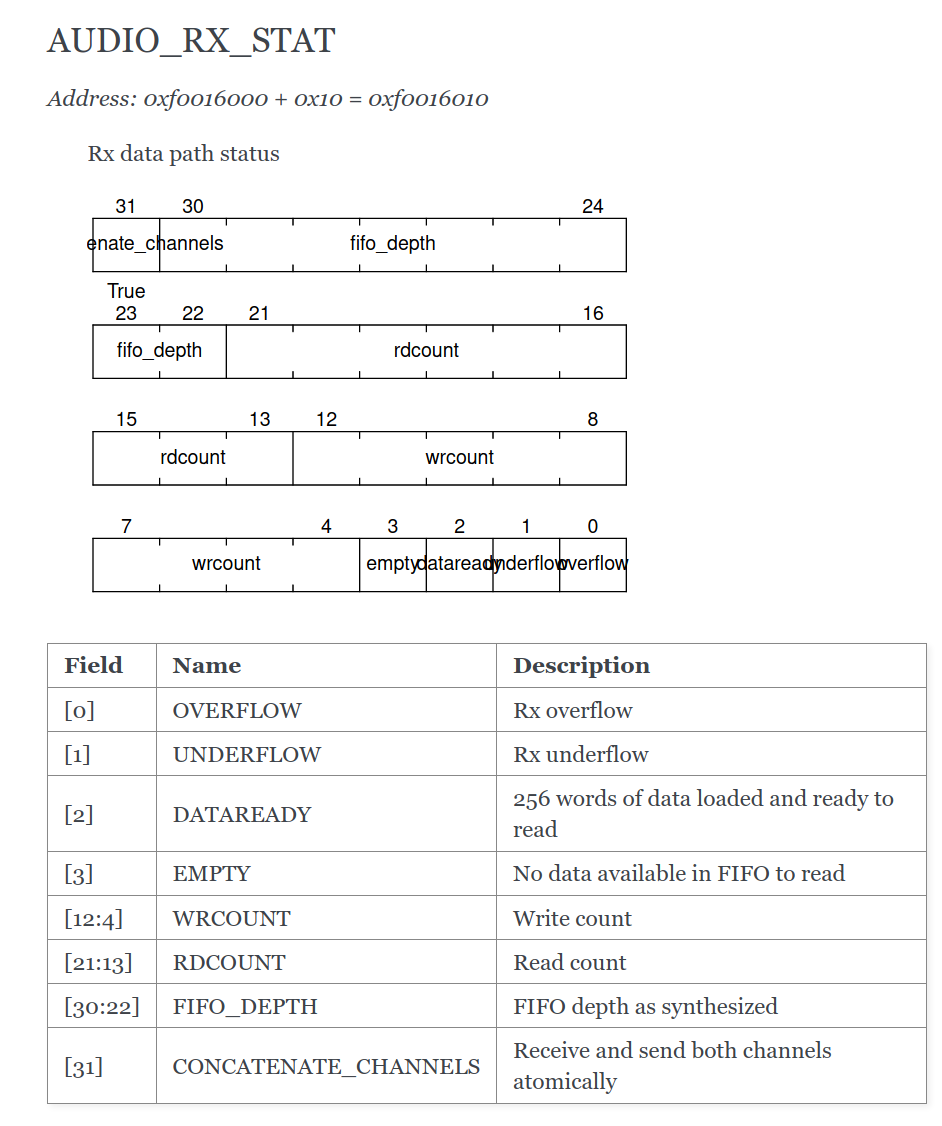

<peripheral>

<name>AUDIO</name>

<baseAddress>0xF0016000</baseAddress>

<groupName>AUDIO</groupName>

<registers>

<register>

<name>RX_STAT</name>

<description><![CDATA[Rx data path status]]></description>

<addressOffset>0x0010</addressOffset>

<resetValue>0x80000000</resetValue>

<size>32</size>

<access>read-only</access>

<fields>

<field>

<name>overflow</name>

<msb>0</msb>

<bitRange>[0:0]</bitRange>

<lsb>0</lsb>

<description><![CDATA[Rx overflow]]></description>

</field>

<field>

<name>underflow</name>

<msb>1</msb>

<bitRange>[1:1]</bitRange>

<lsb>1</lsb>

<description><![CDATA[Rx underflow]]></description>

</field>

<field>

<name>dataready</name>

<msb>2</msb>

<bitRange>[2:2]</bitRange>

<lsb>2</lsb>

<description><![CDATA[256 words of data loaded and ready to read]]></description>

</field>

<field>

<name>empty</name>

<msb>3</msb>

<bitRange>[3:3]</bitRange>

<lsb>3</lsb>

<description><![CDATA[No data available in FIFO to read]]></description>

</field>

<field>

<name>wrcount</name>

<msb>12</msb>

<bitRange>[12:4]</bitRange>

<lsb>4</lsb>

<description><![CDATA[Write count]]></description>

</field>

<field>

<name>rdcount</name>

<msb>21</msb>

<bitRange>[21:13]</bitRange>

<lsb>13</lsb>

<description><![CDATA[Read count]]></description>

</field>

<field>

<name>fifo_depth</name>

<msb>30</msb>

<bitRange>[30:22]</bitRange>

<lsb>22</lsb>

<description><![CDATA[FIFO depth as synthesized]]></description>

</field>

<field>

<name>concatenate_channels</name>

<msb>31</msb>

<bitRange>[31:31]</bitRange>

<lsb>31</lsb>

<description><![CDATA[Receive and send both channels atomically]]></description>

</field>

</fields>

</register>

</registers>

</peripheral>csr_base,audio,0xf0016000,,

csr_register,audio_rx_stat,0xf0016010,1,ro

memory_region,audio,0xe0000000,4,io

let uart_base = (HW_UART_BASE as *mut u32) as *mut Volatile<u32>;

let rx_char: u8 = (*uart_base.add(HW_UART_RXTX)).r() as u8;

(*uart_base.add(HW_UART_RXTX)).ow(tx_char, HW_UART_RXTX_MASK, HW_UART_RXTX_OFFSET);

(*uart_base.add(HW_UART_RXTX))

.rw(tx_char, HW_UART_RXTX_MASK, HW_UART_RXTX_OFFSET)