-

Notifications

You must be signed in to change notification settings - Fork 0

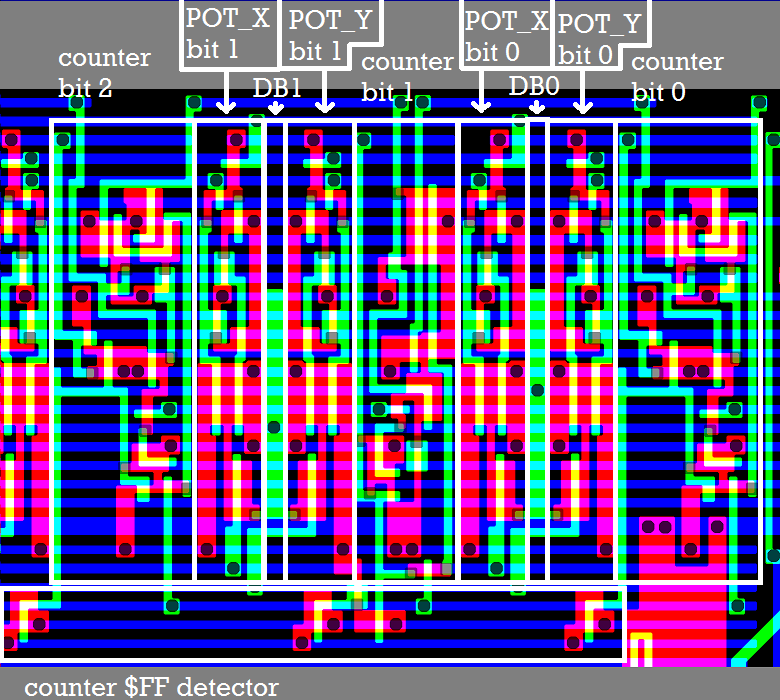

Paddle counter

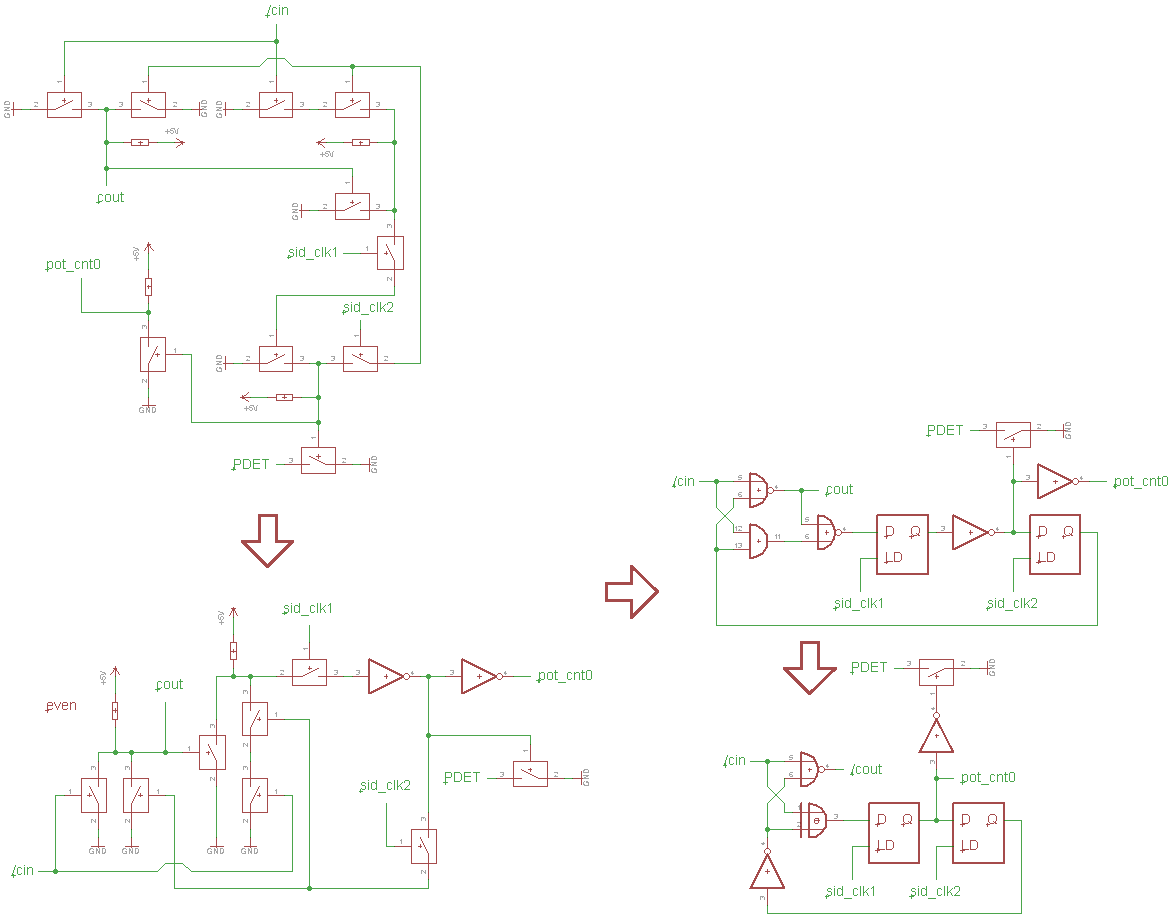

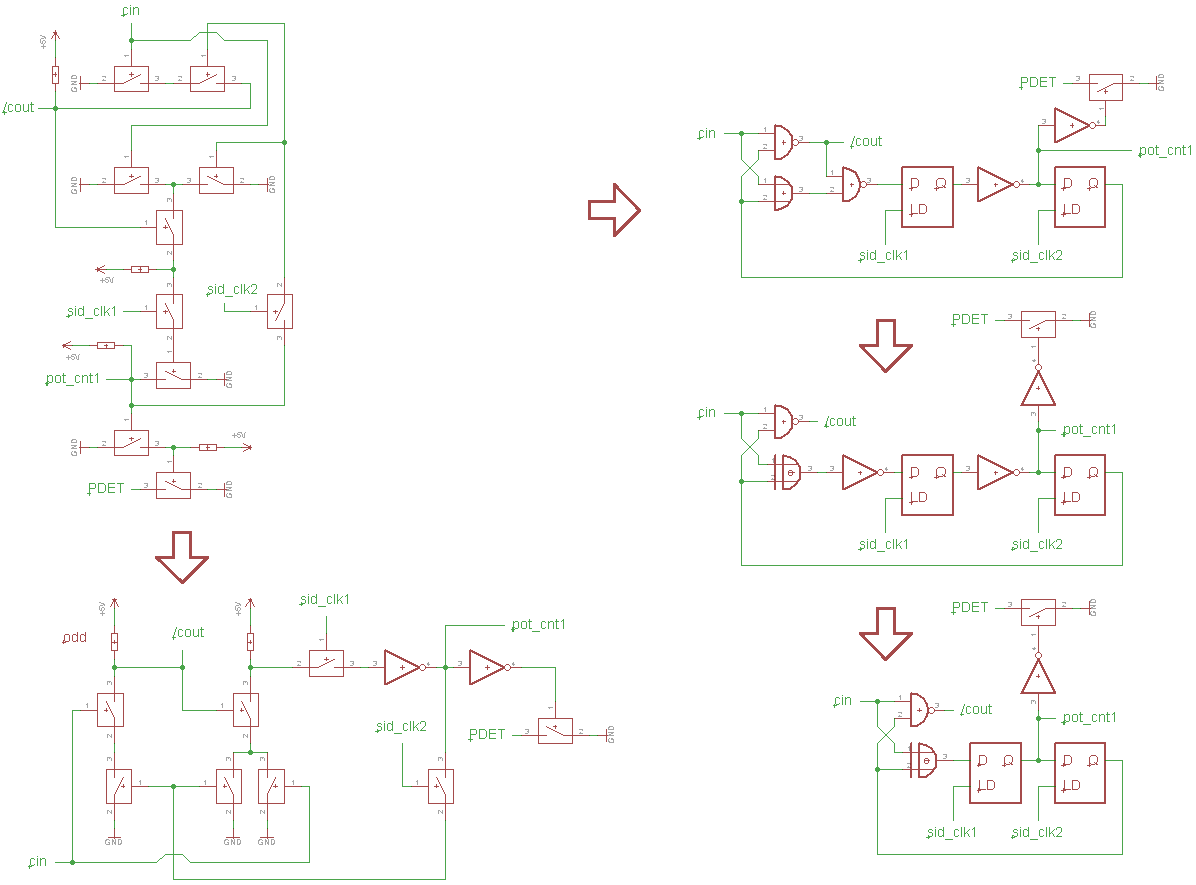

Now for the counter\register block.

Even bits: low_active carry input, high_active carry output, bit is stored in non_inverted form.

Odd bits: high_active carry input, low_active carry output, bit is stored in inverted form.

The signal I had labeled 'PDET' is wired together for counter bit 7..0, with a pullup to +5V. It is 1, when the counter is $FF.

if one or more of the counter bits 7..0 is 0, PDET is tied to GND.

The layout of the paddle counter looks completely different from the layout of the envelope DAC counter, but from the logic level design point of view, the concept for both counters seems to be a little bit similar.

Clock

Reset

Address Decoders

Data Bus

Registers

Oscillator

Pulse Waveform

Triangle Waveform

Noise Generator

Wave Selector

Envelope Overview

Envelope Counter

Sustain Comparator

ADSR registers

Counter Logic

Exponential Divider

LFSR15 counter

LFSR5 counter

Analog stage overview

6581 DACs

6581 Opamps

6581 Filter overview

6581 Audio output

8580 DACs

8580 Virtual ground

8580 AC Voltage divider

8580 Opamps

8580 Filter overview